Vol 12 Issue 03, Sep 2022 ISSN NO: 0364-4308

**YIDDISH**

# Self-Repairable Multiplexer in Real Time for Fault Tolerant Systems

Dr. G C Manjunatha, Kiran P V, Venumadhava M

Assoc. Prof , Asst. Professor, Asst. Professor

gc.manjunatha@gmail.com, pv.kiran1977@gmail.com, venudsp@gmail.com

Department of ECE, Proudhadevaraya Institute of Technology, Abheraj Baldota Rd, Indiranagar,

Hosapete, Karnataka-583225

Abstract— Very large scale integration allows for a greater density of transistors on a single chip. A system or chip becomes increasingly prone to errors as the distance between circuits or transistors decreases. To prevent erroneous findings, fault tolerant mechanisms must be in place. A multiplexer is a piece of equipment that uses a select signal to choose which input signals to use. All of the previous research has focused on self-checking multiplexers. A self-repairing 2:1 multiplexer capable of fixing both temporary and permanent errors is suggested in this study. The self-repairing multiplexer is suggested in two distinct architectural forms. To fix the multiplexer issue, the first design incorporates extra circuitry. Multiplexer components, such as OR and AND gates, are self-repairing in the second design. These multiplexer designs are capable of detecting and fixing both single and multiple problems on their own. All errors are fully recovered by the suggested designs. The functioning of the circuits is confirmed by simulation using the Cadence program.

Index Terms—VLSI, Fault, Error, Self checking, Self repairing.

# I.INTRODUCTION

s the technology is scaling down, chip density is increasing so that millions of transistors are embedded on a single die. The yield may decrease due to process variations, deviation in parameters and lithographic effects [13]. This advanced microelectronic technologies more susceptible

to faults [4].

The response of a circuit may be invalid because of presence of faults [5-8]. This leads to inaccurate results. Fault secure systems are very much needed to withstand faults [910]. So the self checking and repairing is necessary for correct operation of the circuit. In self checking the fault is detected by circuit itself and in self repairing the circuit can repair itself and produces correct output [11]. The overall circuit performance depends on individual gates of the circuit. Using small number of gates for design can increase the performance in terms of delay, area and power.

To get high speed the critical path should be as minimum as possible. Similarly to get low power less number of gates are used at circuit level without compromising the accuracy of the circuit [12-14]. Multiplexers are used in wide variety of applications like adders, multipliers, communication, digital signal processing etc. [15-19] Based on the selection signal multiplexer will select the input data and passes it to the output. The presence of fault in a multiplexer causes invalid data at the output. The multiplexer should be fault secure so that it gives valid data at the output even though faults are present in it. The paper is organized as follows. The self checking multiplexer described in section II, Proposed layout of the self repairing multiplexer 1 and 2 are explained in section III and IV. The layout and equivalent circuit simulation results are discussed in section V. Finally conclusion is given in section VI.

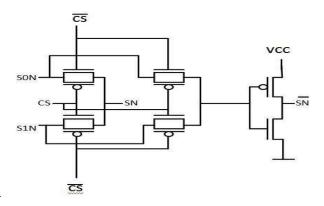

## II.SELFCHECKINGMULTIPLEXER

Self checking multiplexer was proposed in [6]. This self checking multiplexer designed by using four transmission gates and an inverter as shown in Fig. 1. When CS is low S0N is passed to SN. Similarly when CS is high S1N is passed to SN. Thus it implements the function of multiplexer. In this self checking multiplexer when SN and SN\_bar are same then it shows the presence of a fault. By using this structure only fault is detected and can't be repairable. To make the multiplexer self repairing two different structures are

proposed. The CS bar signal is the inverted signal of CS. Fig. 1. checking multiplexer [6].

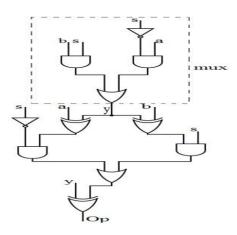

# III.PROPOSEDSELFREPAIRINGMULTIPLEXER1

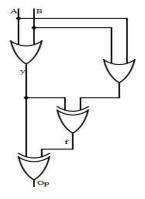

This section describes the proposed self repairing multiplexer1 which uses additional circuitry to detect and repair fault. The circuit diagram is shown in Fig. 2.

Fig. 2. Proposed self repairing multiplexer 1

In Fig. 2 the circuit enclosed in square box shows the basic structure of 2:1 multiplexer. Remaining structure which is not included in the square box is used for repairing the above 2:1 multiplexer. The circuit is able to detect all possible single and multiple faults present in the 2:1 multiplexer and repairs the circuit. The circuit gives 100% error recovery.

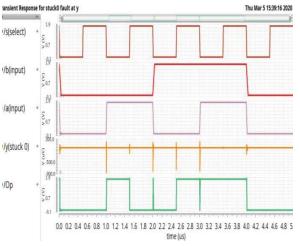

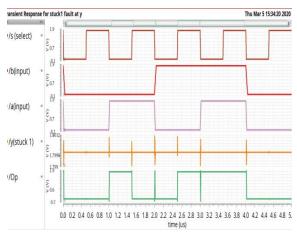

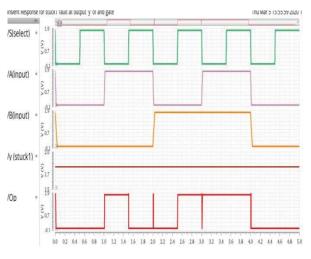

Consider Fig. 2. Assume there is a stuck at '0' fault at y. Since y was stuck at '0', it will give always '0' as the output. However when this value is passed to repairing circuit, it detects the fault and produces correct output. This is shown in Fig. 6. Similarly assume there is a stuck at '1' fault at y. Since y was stuck at '1', it will give always '1' as the output. However when this value is passed to repairing circuit, it detects the fault and produces correct output. This is shown in Fig. 7.

So when there is fault in multiplexer block, then output Op gives the inverted value of y. If there is no fault, then y value is passed to the output Op.

The above proposed multiplexer 1 uses additional circuitry to repair. In the proposed self repairing multiplexer 2 the building blocks of multiplexer itself are self repairable.

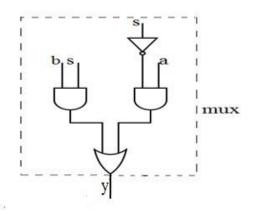

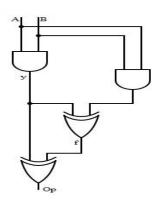

# IV.PROPOSEDSELFREPAIRINGMULTIPLEXER2

The building blocks of this type multiplexer are itself self repairing. The circuit diagram is shown in Fig. 3. In this circuit the logic blocks are self repairing and all the faults are both detectable and repairable. The self repairing structures of AND & OR gate are shown in Fig. 4 and Fig. 5 respectively.

Self

Fig. 3. Proposed self repairing multiplexer 2

Fig. 4. Proposed self repairing AND gate

Fig. 5. Proposed self repairing OR gate

Consider Fig. 4. When there is fault in the AND gate which output is 'y', then f will become logic 1 and circuit gives output Op as inverted value of y. Similarly when there is no fault, then f will give logic 0 and the circuit output Op as the value of y. Similarly consider Fig. 5. When there is fault in the OR gate output Op as inverted value of y. Similarly when there which output is 'y', then f will become logic 1 and circuit gives

# **YIDDISH**

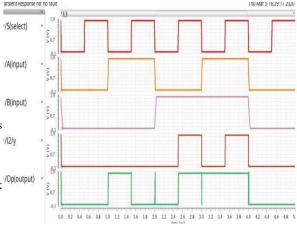

fig. 10. Result of proposed self repairing multiplexer 2 for fault free case

the value of y. Thus any fault can be self repairable by using the self repairing blocks.

#### V. SIMULATIONRESULTS

Fig. 6. Result of proposed self repairing multiplexer 1 for Stufzkult

Fig. 7. Result of proposed self repairing multiplexer 1 for studefult

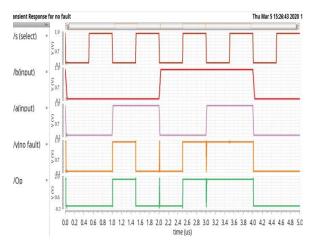

The simulation was done using cadence virtuoso tool using 180nm technology. The voltage of 1.8 V is used for power supply. The result is verified for all the combinations of inputs and all the possible stuck at faults. The proposed structures outputs are reported in Table I. Fig. 6 shows the result of proposed self-repairing multiplexer 1 for stuck '0' fault, Fig. shows result of proposed self repairing multiplexer 1 for stuck '1' fault, Fig. 8 shows result of proposed self repairing multiplexer 1 for fault free case, Fig. 9 shows result of proposed self repairing multiplexer 2 for stuck at '1' fault in AND gate and Fig. 10 shows result of proposed self repairing multiplexer 2 for fault free case respectively.

Fig. 8. Result of proposed self repairing multiplexer 1 for fault free case

Fig. 9. Result of proposed self repairing multiplexer 2 for stuckfamult in AND gate

Vol 12 Issue 03, Sep 2022 ISSN NO: 0364-4308

# **YIDDISH**

Table I

Power, delay and PDP values of the proposed structures.

| Multiplexer  | Proposed self<br>repairing<br>multiplexer 1 | Proposed self<br>repairing<br>multiplexer 2 |

|--------------|---------------------------------------------|---------------------------------------------|

| Power(µW)    | 90.92                                       | 111.5                                       |

| Delay(n sec) | 7.69                                        | 13.12                                       |

| PDP          | 699.36                                      | 1462.88                                     |

#### VI.CONCLUSION

As the multiplexer is very vital component in many systems, faults in multiplexer lead to inaccurate results in the systems. Fault tolerant systems must need fault tolerant multiplexer to avoid faults. The proposed self repairing multiplexers can be used in multiplexers can be used in fault tolerant systems to get 100% error recoverability. The structure repairs itself so that no external inputs are required to repair. This avoids the area overhead. The circuits are simulated and verified the outputs. The fault tolerance of the proposed structures is verified.

### REFERENCES

- [1] Akbar, Muhammad Ali & Lee, Jeong A. (2014). "Self-repairing adder using fault localization" *Microelectronics Reliability*. 54. 10.1016/j.microrel.2014.02.033. -1451.

- [2] Pankaj kumar, Rajendra Kumar Sharma "Real-time fault tolerant full adder design for critical applications" *Engineering Science and Technology*, Volume 19, Issue 3, September 2016, Pages 1465-1472.

- [3] C. Wu, S. Lin, K. Lee and S. M. Reddy, "A Repair-for-Diagnosis Methodology for Logic Circuits," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 26, no. 11, pp. 2254-2267, Nov. 2018

- doi: 10.1109/TVLSI.2018.2856527.

- [4] Koal T, Ulbricht M, Vierhaus HT. Vitual TMR scheme combining fault tolerance and self repair. In: 16<sup>th</sup> Euromicro IEEE conference on digital system design (DSD 2013); 2013. p. 235–42.

- [5] Smith JE, Lam P. A theory of totally self-checking system design. IEEE Trans Comput 1983;C-32:831-44.

- [6] S. gupta, A. Jasuja and R. shandilya, "Real-time fault tolerant full adder using fault localization," 2018 IEEE International Students' Conference on Electrical, Electronics and Computer Science (SCEECS), Bhopal, 2018,pp.1-6. doi: 10.1109/SCEECS.2018.8546908

- [7] Smith JE, Lam P. A theory of totally self-checking system design. IEEE Trans Comput 1983;C-32:831-44.

- [8] Jha NK, Wang S-J. Design and synthesis of self checking VLSI circuits. IEEE Trans Comput – Aided Des Integr Circ Syst 1993;12:878–87. 6.

- [9] Angskun T, Fagg G, Bosilca G, Pjesivac-Grbovic J, Dongarra J. Selfhealing network for scalable fault-tolerant runtime environments. Future Generat Comput Syst 2010;26(3):479–85.

- [10] Majumdar A, Nayyar S, Sengar JS. Fault tolerant ALU system 2012. In: International conference on computing sciences (ICCS); 2012. p. 255–60.

- [11] Fazeli M, Namazi A, Miremadi SG, Haghdoost A. Operand width aware hardware reuse: a low cost fault-tolerant approach to ALU design in embeddedprocessors. Microelectron Reliab 2011;51(12):2374–87.

- [12] Koal T, Scheit D, Schölzel M, Vierhaus HT. On the feasibility of builtin self repair for logic circuits. In: IEEE international symposium on defect and fault tolerance in VLSI and nanotechnology systems; 2011. p. 316–24.

- [13] Khedhiri C, Karmani M, Hamdi B. Concurrent error detection adder based on two paths output computation. In: 2011 Ninth IEEE international symposium on parallel and distributed processing with applications workshops (ISPAW);2011. p. 27–32.

- [14] Mitra S, McCluskey EJ. Which concurrent error detection scheme to choose In: Proceedings IEEE international test conference; 2000. p. 985-94.

- [15] Sarada Musala and Avireni Srinivasulu, "Self testing and fault secure XOR/XNOR circuit using FinFETs" in proc. of the IEEE International Conference on Communication and Signal Processing - ICCSP' 16, Melmaruvathur, Tamilnadu, India, pp. 976-980, April 6-8, 2016. DOI: 10.1109/ICCSP.2016.77543, Scopus Cited.

- [16] Vasudevan DP, Lala PK, Parkerson JP. Self-checking carry-select adder design based on two-rail encoding. IEEE Trans Circ Syst I, Reg Papers 2007;54(12):2696-705.

- [17] B. Sai Krishna, P. Vijaya Lakshmi, Sarada Musala, "Fault Resistant 8Bit Vedic Multiplier Using Repairable Logic", IEEE International Conference on Emerging Trends in Science and Engineering, Sept. 1819, 2019, Scopus Cited.

- [18] Sarada Musala and B.R. Shekara Reddy, "Analysis of low power full adder based on dpl and transmission gates", International conference on innovations in electronics and communication engineering (iciece2014), Guru nanak institute of technology, ibrahimpatnam, July 2014.

- [19] Sarada Musala and B.R. Shekara Reddy, "Implementation of full adder Circuit with New Full swing Ex-OR/Ex-NOR Gates" in proc. of the IEEE Asia-Pacific Conference on Postgraduate Research in Microelectronics and Electronics (PrimeAsia 2013), GITAM University, Visakhapatnam, Dec 19-21, 2013, pp-21.